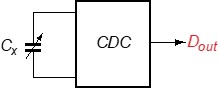

Capacitance-to-Digital Conversion

Publications

- A Readout IC for Capacitive Touch Screen Panels with 33.9 dB Charge-Overflow Reduction Using Amplitude-Modulated Multi-Frequency Excitation

J.-S. An; J.-H. Ra; E. Kang; M. Pertijs; S.-H. Han;

IEEE Journal of Solid-State Circuits,

Volume 56, Issue 11, pp. 3486-3498, November 2021. DOI: 10.1109/JSSC.2021.3100470

Abstract: ...

This paper presents a readout integrated circuit (ROIC) for capacitive touch-screen panels employing an amplitude-modulated multiple-frequency excitation (AM-MFE) technique. To prevent charge overflow, which occurs periodically at the beat frequency of the excitation frequencies, the ROIC modulates the amplitude of the excitation voltages at a mixing frequency derived from the excitation frequencies. Thus, the ROIC can sense the charge signal without charge overflow and maximize the signal-to-noise ratio (SNR) by increasing the amplitude of the excitation voltages up to the sensing range of the readout circuit. The proposed ROIC was fabricated in a 0.13-µm standard CMOS process and was measured with a 32-inch 104×64 touch-screen panel using 1 mm and 10 mm metal pillars. It reduces charge overflow up to 33.9 dB compared to operation without AM-MFE. In addition, the ROIC achieves a frame rate of 2.93 kHz, and SNRs of 41.7 dB and 61.6 dB with 1 mm and 10 mm metal pillars, respectively. - A Capacitive Touch Chipset with 33.9dB Charge-Overflow Reduction using Amplitude-Modulated Multi-Frequency Excitation and Wireless Power and Data Transfer to an Active Stylus

J.-S. An; J.-H. Ra; E. Kang; M. Pertijs; S.-H. Han;

In Dig. Techn. Papers IEEE International Solid-State Circuits Conference (ISSCC),

pp. 430-431, February 2020. - Capacitance-to-digital converter

H. Fan; M. Pertijs; B. A. J. Buter;

Patent, US 10,732,577, August 2020. - A Precision Capacitance-to-Digital Converter with 16.7-bit ENOB and 7.5 ppm/°C Thermal Drift

R. Yang; M. A. P. Pertijs; S. Nihtianov;

IEEE Journal of Solid-State Circuits,

Volume 52, Issue 11, pp. 3018-3031, November 2017. DOI: 10.1109/jssc.2017.2734900

Abstract: ...

This paper presents a high-precision capacitance-to-digital converter (CDC) for displacement measurement in advanced industrial applications, based on a charge-balancing third-order delta–sigma modulator. To achieve high precision, this CDC employs a precision external resistive reference and a quartz-oscillator-based time reference instead of a reference capacitor. To minimize the error contribution of the CDC circuitry, various precision circuit techniques, such as chopping and auto-zeroing, are applied at both system and circuit level. Measurement results of the prototype realized in 0.35-μm CMOS technology show that the CDC achieves an rms resolution of 42 aF across a capacitance range from 6 to 22 pF, corresponding to an effective number of bits (ENOB) of 16.7 bit. The conversion time for one measurement is 10.5 ms, during which the CDC consumes 230 μA from a 3.3-V single supply. The measured thermal stability is within ±7.5 ppm/°C across a temperature range from 20 °C to 70 °C, which represents a significant improvement compared to the state of the art. After a two-point calibration, all ten measured samples from one batch show absolute accuracy below ±25 fF across the entire capacitance measurement range. - A compact sensor readout circuit with temperature, capacitance and voltage sensing functionalities

B. Yousefzadeh; W. Wu; B. Buter; K. Makinwa; M. Pertijs;

In NXP Low-Power Design Conference,

NXP, June 2017.

Abstract: ...

This paper presents an area- and energy-efficient sensor readout circuit, which can precisely digitize temperature, capacitance and voltage. The three modes use only on-chip references and employ a shared zoom ADC based on SAR and ΔΣ conversion to save die area. Measurements on 24 samples from a single wafer show a temperature inaccuracy of ±0.2 °C (3σ) over the military temperature range (-55°C to 125°C). The voltage sensing shows an inaccuracy of ±0.5\%. The sensor also offers 18.7-ENOB capacitance-to-digital conversion, which handles up to 3.8 pF capacitance with a 0.76 pJ/conv.-step energy-efficiency FoM. It occupies 0.33 mm² in a 0.16 μm CMOS process and draws 4.6 μA current from a 1.8 V supply. - A Compact Sensor Readout Circuit with Combined Temperature, Capacitance and Voltage Sensing Functionality

B. Yousefzadeh; W. Wu; B. Buter; K. A. A. Makinwa; M. Pertijs;

In Dig. Techn. Paper IEEE Symposium on VLSI Circuits (VLSI),

IEEE, pp. 1‒2, June 2017. DOI: 10.23919/VLSIC.2017.8008555

Abstract: ...

This paper presents an area- and energy-efficient sensor readout circuit, which can precisely digitize temperature, capacitance and voltage. The three modes use only on-chip references and employ a shared zoom ADC based on SAR and ΔΣ conversion to save die area. Measurements on 24 samples from a single wafer show a temperature inaccuracy of ±0.2 °C (3σ) over the military temperature range (-55°C to 125°C). The voltage sensing shows an inaccuracy of ±0.5\%. The sensor also offers 18.7-ENOB capacitance-to-digital conversion, which handles up to 3.8 pF capacitance with a 0.76 pJ/conv.-step energy-efficiency FoM. It occupies 0.33 mm² in a 0.16 μm CMOS process and draws 4.6 μA current from a 1.8 V supply. - A Compact Sensor Readout Circuit with Combined Temperature, Capacitance and Voltage Sensing Functionality

B. Yousefzadeh; W. Wu; B. Buter; K. A. A. Makinwa; M. Pertijs;

In Dig. Techn. Paper IEEE Symposium on VLSI Circuits (VLSI),

IEEE, pp. 1‒2, June 2017. DOI: 10.23919/VLSIC.2017.8008555

Abstract: ...

This paper presents an area- and energy-efficient sensor readout circuit, which can precisely digitize temperature, capacitance and voltage. The three modes use only on-chip references and employ a shared zoom ADC based on SAR and ΔΣ conversion to save die area. Measurements on 24 samples from a single wafer show a temperature inaccuracy of ±0.2 °C (3σ) over the military temperature range (-55°C to 125°C). The voltage sensing shows an inaccuracy of ±0.5\%. The sensor also offers 18.7-ENOB capacitance-to-digital conversion, which handles up to 3.8 pF capacitance with a 0.76 pJ/conv.-step energy-efficiency FoM. It occupies 0.33 mm² in a 0.16 μm CMOS process and draws 4.6 μA current from a 1.8 V supply. - A 0.05mm² 1V capacitance-to-digital converter based on period modulation

Y. He; Z. Y. Chang; L. Pakula; S. H. Shalmany; M. Pertijs;

In Dig. Techn. Papers IEEE International Solid-State Circuits Conference (ISSCC),

IEEE, pp. 486‒487, February 2015. DOI: 10.1109/ISSCC.2015.7063138

Abstract: ...

This paper presents a digitally assisted period modulation (PM)-based capacitance-to-digital converter (CDC) that is >9× smaller than prior CDCs with >10b resolution, and improves the energy efficiency by >10× compared to previous PM-based CDCs. This is achieved with the help of a piece-wise charge transfer technique that eliminates the need for a large on-chip integration capacitor, a dual-integration-capacitor scheme that reduces the front-end noise contribution, a sampled-biasing technique that reduces the noise of the integration current, and a current-efficient inverter-based design. - Capacitive sensor interface with precision references

R. Yang; M. A. P. Pertijs; S. Nihtianov; P. Haak;

In Proc. IEEE International Conference on Industrial Technology (ICIT),

IEEE, pp. 358‒390, March 2014. DOI: 10.1109/icit.2014.6894896 - A 1.2-V 8.3-nJ CMOS humidity sensor for RFID applications

Z. Tan; R. Daamen; A. Humbert; Y. V. Ponomarev; Y. Chae; M. A. P. Pertijs;

IEEE Journal of Solid-State Circuits,

Volume 48, Issue 10, pp. 2469‒2477, October 2013. DOI: 10.1109/jssc.2013.2275661

Abstract: ...

This paper presents a fully integrated CMOS humidity sensor for a smart RFID sensor platform. The sensing element is a CMOS-compatible capacitive humidity sensor, which consists of top-metal finger-structure electrodes covered by a humidity-sensitive polyimide layer. Its humidity-sensitive capacitance is digitized by an energy-efficient capacitance-to-digital converter (CDC) based on a third-order delta-sigma modulator. This CDC employs current-efficient operational transconductance amplifiers based on current-starved cascoded inverters, whose limited output swing is accommodated by employing a feedforward loop-filter topology. A programmable offset capacitor is included to remove the sensor's baseline capacitance and thus reduce the required dynamic range. To reduce offset errors due to charge injection of the switches, the entire system is auto-zeroed. The proposed humidity sensor has been realized in a 0.16- μm CMOS technology. Measurement results show that the CDC performs a 12.5-bit capacitance-to-digital conversion in a measurement time of 0.8 ms, while consuming only 8.6 μA from a 1.2-V supply. This corresponds to a state-of-the-art figure-of-merit of 1.4 pJ/conversion-step. Combined with the co-integrated humidity sensing element, it provides a resolution of 0.05\% RH in the range from 30\% RH to 100\% RH while consuming only 8.3 nJ per measurement, which is an order-of-magnitude less energy than the state-of-the-art. - Energy-Efficient Capacitive Sensor Interfaces

Zhichao Tan;

PhD thesis, Delft University of Technology, June 2013.

document - An energy-efficient 15-bit capacitive-sensor interface based on period modulation

Z. Tan; S. H. Shalmany; G. C. M. Meijer; M. A. P. Pertijs;

IEEE Journal of Solid-State Circuits,

Volume 47, Issue 7, pp. 1703‒1711, July 2012. DOI: 10.1109/jssc.2012.2191212

Abstract: ...

This paper presents an energy-efficient capacitive-sensor interface with a period-modulated output signal. This interface converts the sensor capacitance to a time interval, which can be easily digitized by a simple digital counter. It is based on a relaxation oscillator consisting of an integrator and a comparator. To enable the use of a current-efficient telescopic OTA in the integrator, negative feedback loops are applied to limit the integrator's output swing. To obtain an accurate ratiometric output signal, auto-calibration is applied. This eliminates errors due to comparator delay, thus enabling the use of a low-power comparator. Based on an analysis of the stability of the negative feedback loops, it is shown how the current consumption of the interface can be traded for its ability to handle parasitic capacitors. A prototype fabricated in 0.35 μm standard CMOS technology can handle parasitic capacitors up to five times larger than the sensor capacitance. Experimental results show that it achieves 15-bit resolution and 12-bit linearity within a measurement time of 7.6 ms for sensor capacitances up to 6.8 pF, while consuming only 64 μA from a 3.3 V power supply. Compared to prior work with similar performance, this represents a significant improvement in energy efficiency. - Energy-Efficient Capacitive Sensor Interfaces

M. A. P. Pertijs; Z. Tan;

In Nyquist AD Converters, Sensor Interfaces, and Robustness,

Springer Science \& Business Media, October 2012.

Abstract: ...

Capacitive sensor systems are potentially highly energy efficient. In practice, however, their energy consumption is typically dominated by that of the interface circuit that digitizes the sensor capacitance. Energy-efficient capacitive sensor interfaces are therefore a prerequisite for the successful application of capacitive sensors in energy-constrained applications, such as battery-powered devices and wireless sensor nodes. This paper derives lower bounds on the energy consumption of capacitive sensor interfaces. A comparison of these bounds with the state-of-the-art suggests that there is significant room for improvement. Several approaches to improving energy efficiency are discussed and illustrated by two design examples.

document - Energy-Efficient Capacitive Sensor Interfaces

M. Pertijs; Z. Tan;

In Proc. Workshop on Advances in Analog Circuit Design (AACD),

March 2012. invited paper. DOI: 10.1007/978-1-4614-4587-6_8 - A 1.8V 11μW CMOS smart humidity sensor for RFID sensing applications

Z. Tan; R. Daamen; A. Humbert; K. Souri; Y. Chae; Y. V. Ponomarev; M. A. P. Pertijs;

In Proc. IEEE Asian Solid State Circuits Conference (A-SSCC),

IEEE, pp. 105‒108, November 2011. DOI: 10.1109/ASSCC.2011.6123615

Abstract: ...

A fully-integrated humidity sensor for a smart RFID sensor platform has been realized in 0.16μm standard CMOS technology. It consists of a top-metal finger-structure capacitor covered with a humidity-sensitive layer, combined with a micro-power flexible sensor interface based on a second-order incremental delta-sigma converter. The interface can be easily reconfigured to compensate for process variation of the sensing element. In a measurement time of 10.2 ms, the interface performs a 13-bits capacitance-to-digital conversion while consuming only 5.85 μA from 1.8 V supply. In combination with the co-integrated sensor capacitor, it thus provides a humidity-to-digital conversion with a resolution of 0.1\% RH in the range of 20\% to 90\% RH at only 107 nJ per measurement. This represents a significant improvement in energy efficiency compared to existing capacitive-sensor interfaces with comparable performance. - An energy-efficient 15-bit capacitive sensor interface

Z. Tan; M. A. P. Pertijs; G. Meijer;

In Proc. European Solid-State Circuits Conference (ESSCIRC),

IEEE, pp. 283‒286, September 2011. DOI: 10.1109/esscirc.2011.6044962 - Energy-efficient capacitive sensor interface with high dynamic range

Z. Tan; M. A. P. Pertijs; G. C. M. Meijer;

In Annual Sensor Technology Workshop Sense of Contact,

The Netherlands, April 2010.

BibTeX support