# An Energy-Efficient BJT-Based Temperature-to-Digital Converter with ±0.13°C (3σ) Inaccuracy from -40 to 125°C

Rushil K. Kumar, Hui Jiang, and Kofi A. A. Makinwa Delft University of Technology, The Netherlands

Abstract— This paper describes an energy-efficient BJT-based temperature-to-digital converter (TDC) with a state-of-the-art resolution FoM (RFoM) of 5.4pJ·K². It consists of a BJT front-end, a capacitively-coupled instrumentation amplifier (CCIA) and a 2nd-order continuous-time (CT)  $\Delta\Sigma$ ADC. The front-end and the CCIA employ bitstream-controlled dynamic element matching (DEM) and chopping to mitigate mismatch and 1/f noise without incurring quantization noise fold-back. The sensor achieves  $\pm 0.13^{\circ}$ C (3 $\sigma$ ) inaccuracy from -40 to 125 $^{\circ}$ C and has a supply sensitivity of 8.2mK/V.

## I. INTRODUCTION

BJT-based TDCs are widely used, because they only require room-temperature calibration to achieve high accuracy [1-5]. However, they usually employ switched-capacitor (SC) readout architectures, and so their resolution and energy efficiency are limited by kT/C noise. For example, a state-ofthe-art TDC achieves a resolution FoM of 7.8pJ·K<sup>2</sup> [4]. Although the design in [5] is more energy-efficient, achieving 3.6pJ·K<sup>2</sup>, its output is a duty-cycle modulated signal, which must still be sampled by a high-speed clock and digitized by an external counter. This paper describes a TDC that uses a continuous-time approach. A CCIA is used to boost a PTAT voltage  $\Delta V_{be}$  (generated by a BJT front-end) before it is digitized by a CT  $\Delta\Sigma$ ADC. As in SC circuits, the CCIA's gain is also determined by a capacitor ratio, resulting in good accuracy and stability. The TDC achieves  $\pm 0.13$  °C (3 $\sigma$ ) from -40°C to 125°C, and a state-of-the-art RFoM of 5.4pJ·K<sup>2</sup>.

### II. PROPOSED DESIGN

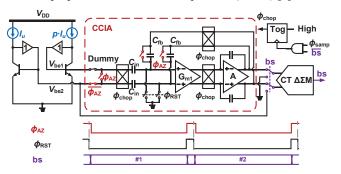

Fig. 1 shows the proposed TDC. A BJT front-end generates PTAT and CTAT voltages  $\Delta V_{be}$  and  $V_{be}$ . The CCIA amplifies  $\Delta V_{be}$  by a factor  $C_{in}/C_{fb} = \alpha/2$ . Its output is then applied to a 2nd-order incremental CT  $\Delta\Sigma$ ADC, which implements a charge-balancing scheme, in which  $2 \cdot \alpha/2 \cdot \Delta V_{be}$  is integrated when the bitstream output (bs) is "0" and  $-V_{be}$  when bs is "1". This results in a bitstream average  $\mu = \alpha\Delta V_{be}/(\alpha\Delta V_{be} + V_{be})$ , which is proportional to absolute temperature (PTAT) [6].

Fig.1 a) Block diagram of the TDC and b) the associated timing.

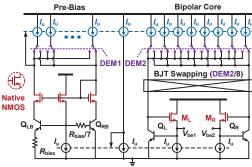

Fig. 2 Simplified schematic of the BJT front-end.

The BJT front-end consists of a bias circuit and a bipolar core (Fig. 2), built around two pairs of identical NPNs (QLB, Q<sub>RB</sub>, Q<sub>L</sub> and Q<sub>R</sub>). Each pair is biased at a collector current ratio of 1:7, with a unit current of 53nA at room temperature. The bias circuit generates a PTAT current that is used by the NPNs of the bipolar core to generate  $V_{be}$  and  $\Delta V_{be}$ . The base currents of the NPNs are provided by source followers M<sub>L</sub> and M<sub>R</sub>, which also drive the input resistors of the CT  $\Delta\Sigma$ ADC without affecting accuracy. To minimize their mismatch, the current sources of the bipolar core and biasing circuit are dynamically matched. As in [6], this is done in a bitstream-controlled manner to avoid quantization noise fold-back due to intermodulation between the DEM residuals and the modulator's bitstream. To mitigate their mismatch, the NPNs of the sensor core are chopped at the end of every complete cycle of DEM2, avoiding the intermodulation.

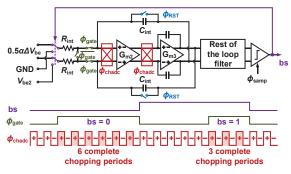

Fig. 3 Block diagram of CT  $\Delta\Sigma$ ADC with the associated timing.

The CCIA consists of a 2-stage Miller-compensated amplifier (Fig. 1). It employs a current-reuse input stage for energy efficiency. Its closed-loop gain is set to  $\alpha/2$  (=7), which limits its output swing to  $\sim$ 0.5V over the full temperature range and ensures that its loop-gain is high enough to keep its gain spread below 0.01%. Two CMFB loops (not shown) ensure

adequate robustness to process and temperature variations. The CCIA is also chopped in a bitstream-controlled manner.

At the start of each incremental conversion, the opamp is auto-zeroed by shorting its feedback caps  $C_{\rm fb}$  ( $\phi_{\rm AZ}$ , Fig. 1) [7]. This effectively stores the opamp's offset on the input caps  $C_{\rm in}$ , resulting in significantly reduced chopping ripple. Therefore, a ripple reduction loop is not required.

At the chopping transitions, the CCIA generates output spikes, which would be a source of error. To avoid this, the input of the 1st integrator of the  $\Delta\Sigma$ ADC is gated as in [8] (Fig. 3). Furthermore, the integrator is chopped at  $8f_s$  to suppress its 1/f noise and offset. This choice ensures that the chopped offset is always averaged out despite the different lengths of the integration windows corresponding to bs=0 and bs=1 (Fig. 3). To conserve area, the 2nd integrator and feed-forward coefficient are implemented with SC techniques.

### III. MEASUREMENT RESUTLS

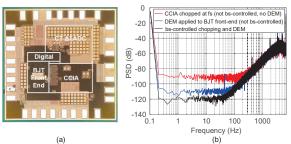

Fig. 4 a) Die micrograph of the TDC, b) PSD of the TDC's bitstream.

Fabricated in a standard 180nm CMOS process, the TDC occupies an active area of 0.35mm² (Fig. 4a) and consumes 5.6μA from a 1.6V supply at room temperature. The sinc² decimation filter is implemented off-chip. As shown in Fig. 4b, the use of bitstream-controlled chopping and DEM effectively prevents quantization noise fold-back and preserves the noise floor of the BJT front-end.

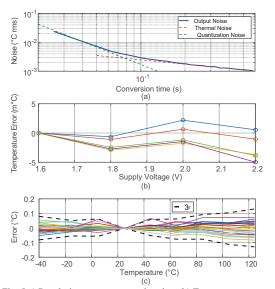

Fig. 5 a) Resolution versus conversion time, b) Temperature error versus supply voltage, and c) Inaccuracy of 25 devices.

When sampled at  $f_s = 15.625$ kHz, the TDC achieves a resolution of 1.67mK (rms) in a conversion time of 218ms (Fig. 5a). From 1.6V to 2.2V, its supply sensitivity is 8.2mK/V (Fig. 5b). Measurements were made on 25 devices in ceramic DIL packages. To compensate for  $V_{be}$  spread, each sample was calibrated at 25°C. In the same step, the CCIA gain ( $C_{in}/C_{fb}$ ) of each sample is calibrated with the help of an external voltage. This information is used by the digital backend to perform a PTAT trim on each sample, resulting in an inaccuracy of  $\pm 0.25$ °C (3 $\sigma$ ) from -40°C to 125°C. This improves to  $\pm 0.13$ °C (3 $\sigma$ ) after a 5<sup>th</sup> order polynomial is used to remove systematic non-linearity (Fig. 5c). In Table I, the performance of the TDC is summarized and compared with previous BJT-based designs. As can be seen, this work achieves both competitive accuracy and state-of-the-art energy-efficiency.

Table I. Performance summary and comparison with the state-of-the-art.

|                                         | JSSC2013<br>[1]   | JSSC2015<br>[2]  | IEEE SJ 2017<br>[3] | JSSC2017<br>[4]   | This work         |

|-----------------------------------------|-------------------|------------------|---------------------|-------------------|-------------------|

| Technology                              | 0.16µm            | 0.16µm           | 0.18µm              | 0.16µm            | 0.18µm            |

| Chip area [mm²]                         | 0.54              | 0.085            | 0.198               | 0.16              | 0.35              |

| Supply voltage [V]                      | 1.6               | 1.4              | 1                   | 1.5-2             | 1.6-2.2           |

| Supply current [µA]                     | 3.4               | 4.5              | 1.1                 | 5                 | 5.6               |

| Supply sensitivity (m°C/V)              | 500               |                  |                     | 10                | 8.2               |

| Temperature range                       | -55°C to<br>125°C | -40°C to<br>85°C | 25°C to 45°C        | -55°C to<br>125°C | -40°C to<br>125°C |

| 3σ inaccuracy [°C]<br>(Trimming points) | ±0.2 (1)          | -                | ±0.2 (1)            | ±0.06 (1)         | ±0.13 (1)         |

| Conversion time [ms]                    | 5.3               | 6                | 500                 | 5                 | 218               |

| Resolution [mK]                         | 20                | 25               | 10                  | 15                | 1.67              |

| Resolution FoM [pJ·K <sup>2</sup> ] *   | 11                | 24               | 55                  | 7.8               | 5.4               |

<sup>\*</sup> Resolution FoM = Energy / (Conversion x (Resolution)<sup>2</sup>)

#### REFERENCES

- [1] K. Souri, Y. Chae, K. A. A. Makinwa, "A CMOS temperature sensor with a voltage-calibrated inaccuracy ±0.15 °C (3σ) from -55 °C to +125 °C," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 1, pp. 292–301, Jan. 2013.

- [2] S. Zaliasl, et al., "A 3 ppm  $1.5\times0.8$  mm2  $1.0~\mu$ A 32.768 kHz MEMS-based oscillator," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 1, pp. 291–302, Jan. 2015.

- [3] M. Law et al., "A 1.1 μW CMOS Smart Temperature Sensor With an Inaccuracy of ±0.2 °C (3σ) for Clinical Temperature Monitoring", IEEE Sensors Journal, vol. 16, no. 8, Apr. 2016.

- [4] B. Yousefzadeh, S.H. Shalmany, K.A.A. Makinwa, "A BJT based temperature-to-digital converter with ±60 mK (3σ) inaccuracy from -55 °C to +125 °C in 0.16 μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 4, pp. 1044–1052, Apr. 2017.

- [5] A.Heidary; G.Wang; K.A.A.Makinwa; G.Meijer, "A BJT-based CMOS temperature sensor with a 3.6pJ·K2-resolution FoM," 2014 IEEE International Solid-State Circuits Conference (ISSCC),pp. 224–225, 2014.

- [6] M.A.P. Pertijs et al., "A CMOS smart temperature sensor with a 3σ inaccuracy of ±0.5 °C from -50 °C to +120 °C," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 2, pp. 454–461, Jan. 2005.

- [7] H. Wang et al., "A 19 nV/√Hz Noise 2-μV Offset 75-μA Capacitive-Gain Amplifier With Switched-Capacitor ADC Driving Capability," in IEEE Journal of Solid-State Circuits, vol. PP, no. 99, pp. 1-10, Aug.2017.

- [8] H. Jiang, S. Nihtianov and K. A. A. Makinwa, "An Energy-Efficient 3.7-nV/√Hz Bridge Readout IC With a Stable Bridge Offset Compensation Scheme," in *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 856-864, March 2019.